VOICE OF THE ENGINEER

MARCH 6 Issue 5/2008 www.edn.com

R

Supply Chain: Avnet's Harley Feldberg Pg 72

Signal Integrity: A very special value Pg 24

Tapeout: Know your IP provider Pg 26

Design Ideas Pg 61

Tales from the Cube: Power, power everywhere Pg 80

# CONSUMER ICS: DESIGNING FOR RELIABILITY

**MOBILE TELEVISION:** FREE—AND LOCATION-FREE

Page 29

DESIGNING WITH QDRII+ AND QDRII IN ONE SYSTEM

Page 47

FLYBACK TRANSFORMER ENABLES HIGH POWER-FACTOR AND CONVERTER EFFICIENCY

CLICK HERE TO **START** a FREE <u>e-newsletter</u> subscription

CLICK HERE TO **RENEW** your FREE magazine subscription

Page 51

# Hear the Difference

# First Closed-Loop, Digital-Input Class-D Amp

| Device  | Power   | Closed-Loop | Control          | Audio Processing |  |

|---------|---------|-------------|------------------|------------------|--|

| TAS5706 | 2 x 20W | Yes         | l <sup>2</sup> C | Yes              |  |

| TAS5704 | 2 x 20W | Yes         | Hardwired        | No               |  |

The **TAS5706** and **TAS5704** from Texas Instruments are the industry's first digital-input, stereo Class-D speaker amplifiers with integrated feedback. Their closed-loop architecture produces a richer, more accurate sound and lowers total system cost. And, both ICs feature end-to-end digital performance and a graphical development environment for easier design. **That's High-Performance Analog>>Your Way™**.

#### www.ti.com/tas5706 1.800.477.8924 ext. 5706

More than 300,000 products stocked and ready to ship today!"

Digi-Key Corporation purchases all product directly from its original manufacturer.

Quality Electronic Components, Superior Service

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

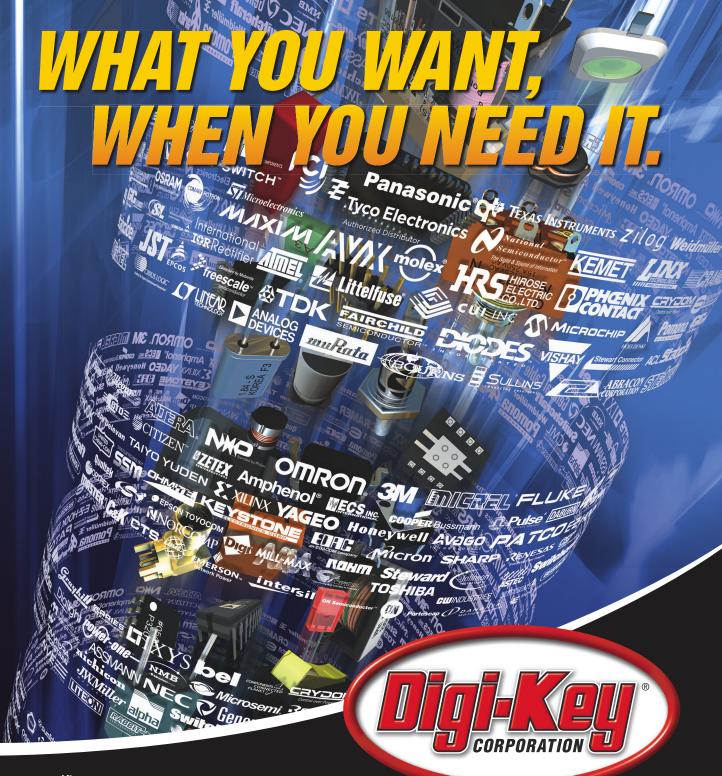

# SuperH Flash Microcontroller reaches speeds up to 160MHz

Superscalar performance, high-speed on-chip FLASH memory access, and much more

# **Renesas Technology**

# No.1\* supplier of microcontrollers in the world

proudly presents the SuperH Family of devices. SuperH devices equipped with the SH-2A core offer superscalar performance at speeds of 160MHz, allowing high-speed access to on-chip FLASH memory and up to 200MHz CPU performance (ROMless devices). Enhanced features that include on board Floating Point Unit (FPU), Multiply Accumulate Unit (MAC), High-Speed Barrel Shifter and advanced addressing modes deliver DSP-like performance in RISC style architecture without the complicated programming associated with a DSP engine. The SuperH RISC engine and the SH-2A core are establishing new performance standards in the industry, and are ideal for systems that demand real-time, high-precision control and require a combination of high performance CPU with high-speed flash.

#### SuperH MCU Lineup

## Dhrystone MIPS at MHz Superscalar Performance - Two instructions are executed per cycle at 160MHz - World's fastest embedded FLASH with 12.5ns read

access time.

#### Fast Real-Time Control

- Register Bank architecture (15 Banks) for context switching enables 37.5nsec (6 cycles) interrupt latency time.

## High Integration

- 512KB On-Chip Flash / 32KB On-Chip RAM - Advanced 16-bit PWM timers to drive two motors simultaneously

- 1.25 µ sec 12-bit A/D conversion with 3 sample & hold circuits

\*Source: Gartner (March 2007) "2006 Worldwide Microcontroller Vendor Revenue" GJ07168

RenesasTechnologyCorp.

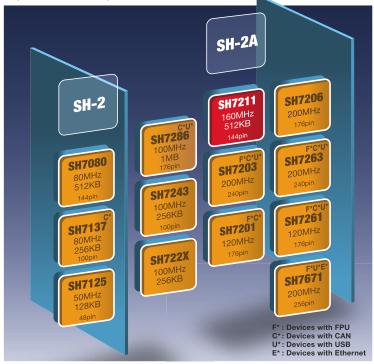

# **Delta-Sigma ADCs**

# High Performance, Broad Portfolio – Enable Your Design

# - High-Performance Analog>>Your Way™

Low noise. Wide bandwidth. High speed. When your design needs best-in-class delta-sigma ADC peformance, look to TI for high-performance devices to meet your design challenges.

| Device  | Description                                                                                                                              |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADS1110 | Tiny, low power, 16-bit $\Delta\Sigma$ ADC with onboard reference and PGA (G=1, 2, 4, 8) in SOT: 2.048V ±0.05% accuracy, 5ppm/°C drift   |  |  |  |

| ADS1226 | Low-cost, easy-to-use 24-bit $\Delta\Sigma$ ADC: dedicated START pin, 100SPS data rate, 4µV <sub>RMS</sub> low noise                     |  |  |  |

| ADS1232 | Ideal for weigh scales: 24-bit $\Delta\Sigma$ ADC, up to 23.5 effective bits, onboard PGA (G = 1, 2, 64, 128), 10SPS or 80SPS data rates |  |  |  |

| ADS1256 | Best-in-class 23-bit, noise-free $\Delta\Sigma$ ADC: 8 channels, 30kSPS and programmable digital filter (averaging)                      |  |  |  |

| ADS1258 | Fastest channel cycling, 24-bit, 125kSPS $\Delta\Sigma$ ADC: Measure all 16 channels in <675 $\mu$ s                                     |  |  |  |

| ADS1278 | Widest bandwidth, simultaneous sampling: 24-bit, 8-channel $\Delta\Sigma$ ADC, 128kSPS, 106dB SNR, ±0.0003% INL                          |  |  |  |

| ADS1281 | Ultra-low distortion 24-bit $\Delta\Sigma$ ADC: 130dB SNR and –122dB THD while consuming only 12mW of power, ±0.00006% INL               |  |  |  |

| ADS1610 | Fastest 16-bit $\Delta\Sigma$ ADC: 10MSPS, 86dB SNR, 5MHz wide and flat bandwidth                                                        |  |  |  |

| DDC232  | Highly integrated, current-input 20-bit $\Delta\Sigma$ ADC for measuring photodiodes, X-ray security and CT scanners: 32 channels        |  |  |  |

www.ti.com/deltasigma 1.800.477.8924 ext. 1434 — Get Datasheets, Samples and Evaluation Modules

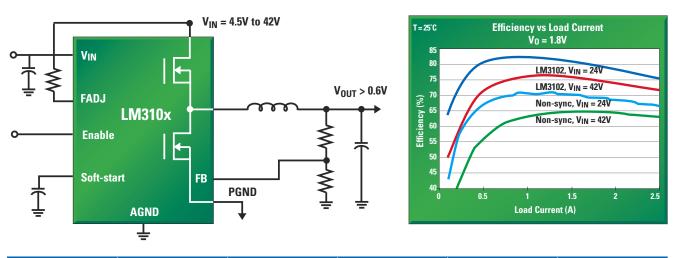

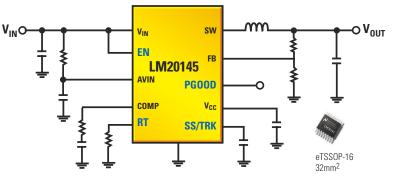

# PowerWise<sup>®</sup> 2.5A, 42V SIMPLE SWITCHER<sup>®</sup> Synchronous Step-Down Regulators

national.com/switcher

# Constant-on-Time (COT) LM310x Regulators are Energy-Efficient and Need No Loop Compensation and Are Stable with Ceramic Capacitors

| Product ID | V <sub>IN</sub> Range (V) | Current (A) | V <sub>FB</sub> (V) | Frequency (MHz) | Packaging |

|------------|---------------------------|-------------|---------------------|-----------------|-----------|

| LM3100     | 4.5 to 36                 | 1.5         | 0.8                 | Up to 1         | eTSSOP-20 |

| LM3102     | 4.5 to 42                 | 2.5         | 0.8                 | Up to 1         | eTSSOP-20 |

| LM3103     | 4.5 to 42                 | 0.75        | 0.6                 | Up to 1         | eTSSOP-16 |

# LM310x Features

- COT control provides lightning-fast transient response

- Stable with ceramic capacitors

- Near-constant frequency operation from unregulated supplies

- No loop compensation reduces external component count

- Pre-bias startup

- Discontinuous Conduction Mode (DCM) operation for a light load

- Enabled in National's WEBENCH® online design environment

## **Applications**

Embedded systems, industrial controls, automotive telematics and body electronics, point-of-load regulators, storage systems, and broadband infrastructure

For samples, datasheets, online design tools, and more information about PowerWise products, visit:

national.com/switcher Or call: 1-800-272-9959

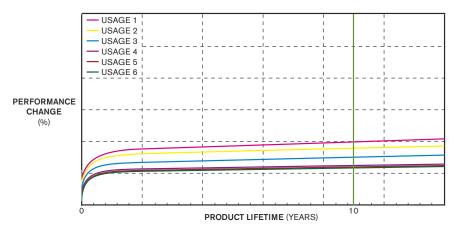

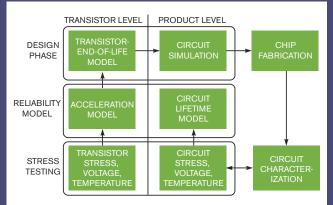

# Consumer ICs: designing for reliability

38 Consumers want the latest electronics but only if they'll last longer than the time it takes to take them out of their packages. IC vendors must tackle reliability issues so that their devices will find use in reliable, long-lasting products. by Michael Santarini, Senior Editor

# Mobile television: free—and location-free

29 If you think cellular's the only way you'll catch on-the-go television in the future, think again. Over-the-air broadcasters and satellite-based-service providers hope to catch the mobile-TV wave and ride it to fiscal success. *by Brian Dipert,*

Senior Technical Editor

# **EDN** contents 3.6.08

# Designing with QDRII+ and QDRII in one system

Although the latest QDRII+-SRAM devices offer speeds as much as 50% higher than QDRII products, a properly designed board can support either architecture. *by Jayasree Nayar, Cypress Semiconductor*

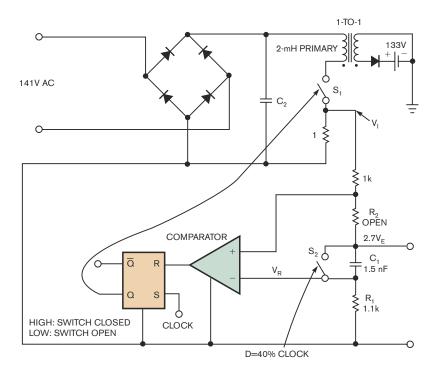

# Flyback transformer enables high powerfactor and converter efficiency

51 Ever-tightening regulations require a power factor of at least 0.9 and high efficiency for offline power supplies. This new switching-converter topology uses a flyback transformer and accomplishes both these goals in one stage.

by Cecil Deisch, Tellabs Operations Inc

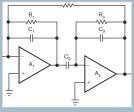

# DESIGNIDEAS

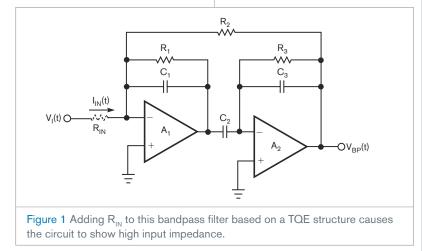

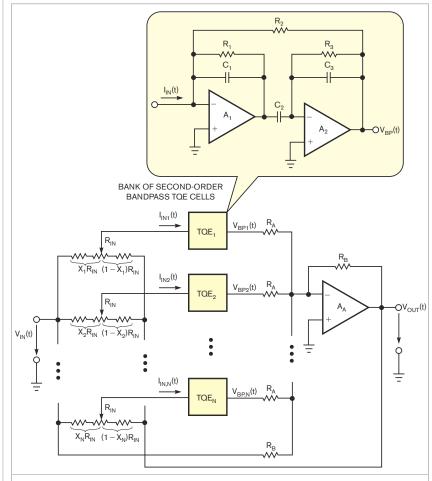

- 61 Audio equalizer features transimpedance Q-enhancement topology

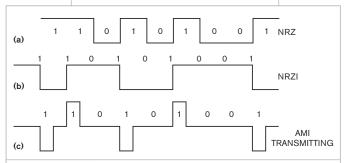

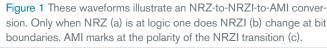

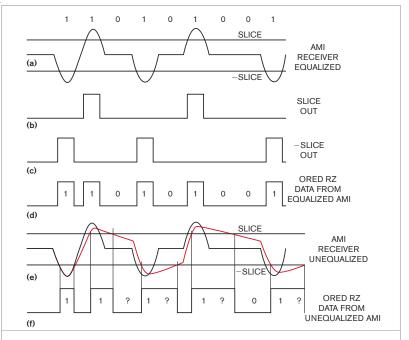

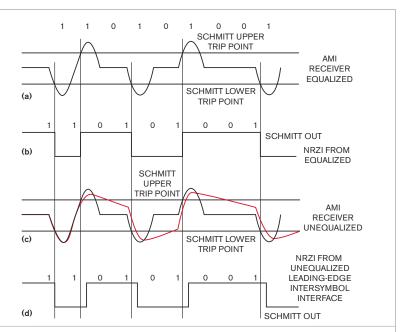

- 66 AMI-to-NRZI-direct-conversion circuit tolerates unequalized pulse tails

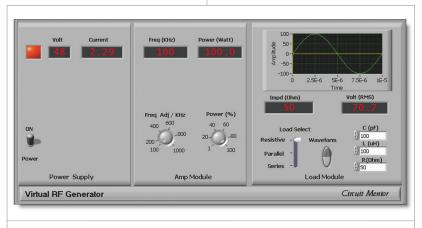

- 70 Virtual RF generator measures load impedance and power

- Send your Design Ideas to edndesignideas@reedbusiness.com.

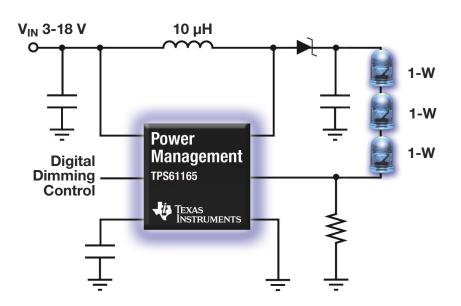

# High-Brightness LED Driver 38-V, 1.2-A Switch Boost Converter

- High-Performance Analog>>Your Way™

# Applications

- High-power LEDs used in singlecell, battery-powered applications or point-of-load designs with a 9-V or 12-V bus

- White LED backlighting for media form factors up to 9"

- Ultra-mobile PCs

- LCD photo frames

- Industrial laser diodes

- Medical and industrial lighting

# **Features**

- Wide input voltage range up to 18V

- Integrated 38-V, 1.2-A highefficiency switching FET

- 1.2-MHz switching frequency

- 200-mV reference voltage with 2% accuracy

- 90% power efficiency

- 32-step, single-wire digital dimming or PWM dimming

- 2mm x 2mm x 0.8mm, 6-pin

QFN with thermal pad

The **TPS61165** is the first high-output power boost converter that can drive up to three 1-watt LEDs in series. The tiny power circuit can manage backlight LEDs for media form factor displays up to 9 inches in diameter.

# White LED Drivers that Support 3 to 12 LEDs

| Device    | Topology    | # of<br>LEDs | V <sub>IN</sub> (V) | Switch<br>Current<br>Limit (A) | V <sub>OUT</sub> | Efficiency<br>(%) | Package   | Price<br>(1k)* |

|-----------|-------------|--------------|---------------------|--------------------------------|------------------|-------------------|-----------|----------------|

| TPS61160  | Boost       | 6            | 2.7 to 18           | 0.7                            | 27               | 90                | 2 x 2 QFN | \$0.85         |

| TPS61161  | Boost       | 10           | 2.7 to 18           | 0.7                            | 38               | 90                | 2 x 2 QFN | \$1.00         |

| TPS61165  | Boost       | 10           | 3.0 to 18           | 1.2                            | 38               | 90                | 2 x 2 QFN | \$1.45         |

| TPS61081  | Boost       | 7            | 2.5 to 6            | 1.6                            | 27               | 87                | 3 x 3 QFN | \$1.45         |

| TPS61150A | Boost       | 6 x 2        | 2.5 to 6            | 0.7                            | 27               | 85                | 3 x 3 QFN | \$1.65         |

| TPS60251  | Charge Pump | 5+2+1        | 2.7 to 6.5          | -                              | 6.5              | 90                | 4 x 4 QFN | \$1.40         |

| TPS40211  | Boost       | 12 x 10      | 4.5 to 52           | 6.0                            | 5 to 250         | 90                | 3 x 3 SON | \$1.10         |

\* Suggested resale price in U.S. dollars in quantities of 1,000.

www.ti.com/tps61165 1.800.477.8924 ext. 4352 Get Evaluation Modules, Samples and New LED Drivers Catalog

# **contents** 3.6.08

Dilbert 18

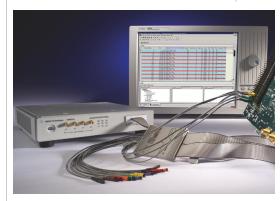

- 17 Logic-analyzer-based instruments debug, validate MIPI physical layer

- 18 Magma offers DRC-incremental Talus

- 20 Open Verification Methodology is ready for download from Cadence, Mentor

- 20 Network-media player drives multiple displays

- 22 **Research Update:** Fiber-based energy harvester potentially turns garments into generators; Coolcuring polymer simplifies IC fabrication; Holographic display has a refresh rate of minutes

# DEPARTMENTS & COLUMNS

- 10 EDN.comment: Fractal engineering versus synergy

- 24 Signal Integrity: Z<sub>MIN</sub>, a very special value

- 26 Tapeout: Know your IP provider

- 72 **Supply Chain:** Demand grows for distributordemand creation; Application processors face falling unit prices; Ontario begins WEEE directive compliance

- 80 Tales from the Cube: Power, power everywhere, but nary a watt to blink

# PRODUCT ROUNDUP

- 75 **Power Sources:** Rectifier modules, ac/dc power adapters, wall-mount rectifier systems, POL converters, switchers, and more

- 76 Integtrated Circuits: ADCs, 16-channel analog switches, and powerline-communications chips

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional maling offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Bav, 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Bav, 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2008 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issue: US, \$165 one year, (anada, \$226 one year, (includes 7% GST, GST#123397457), Weico, \$215 one year, air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian address to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 58, Number 5 (Printed in USA).

# All the right tools in your hand.

# WaveJet<sup>®</sup> Oscilloscopes

# More tools. Better tools. The right tools.

The right tools make debugging faster and easier. The WaveJet 300 Series provides more tools and greater performance than other compact oscilloscopes in the 100 MHz to 500 MHz range.

iC1MΩ

- · Long Memory: 500 k/ch

- Large 7.5" Color Display

- · Compact Size, only 4" Deep

- USB Connectivity

- Replay History Mode

- Frequency Counter

# online contents

HOME

#### NEWS CENTER

#### DESIGN CENTERS BUSINESS CENTERS

PART SEARCH M

## ONLINE ONLY

Check out these Web-exclusive articles:

#### Innovation Awards Finalists

Read all about the finalists in *EDN*'s 18th Annual Innovation Awards. The online voting has closed, but you can learn all about the would-be winners—and get tickets for the awards event taking place on April 14. →www.edn.com/innovation18

#### Using optical feedback to design a more robust high-brightness-LED system

→www.edn.com/article/CA6527085

Reducing buck converter input capacitance through multiphasing and clock synchronization

→www.edn.com/article/CA6522515

Where's the ROI in DFM? →www.edn.com/article/CA6531948

A solar panel on every building → www.edn.com/article/CA6524103

Nokia's Internet tablets: certainly not iPhone clones →www.edn.com/080306toc1

Wii hacks put PS3 and Xbox360 to shame →www.edn.com/080306toc2

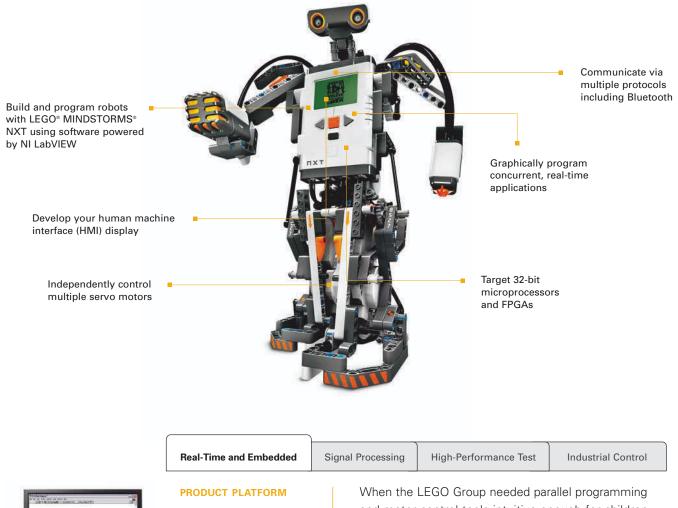

Serious toys →www.edn.com/080306toc3

Electroluminescent sheets conjure up window where none exists →www.edn.com/080306toc4

Are MIT graduates nerds or geeks? →www.edn.com/080306toc5

# READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

# Mobile television: strong, weak, or zero reception?

On-the-go TV is here; some contend that it's been here for a while. Meanwhile, the number of "third-screen" options is rapidly expanding—from gear that fits into your palm to an LCD in the back seat of your car. But is anyone watching? →www.edn.com/article/CA6526814

Dealing with the devil: Could REACH be better than ROHS? →www.edn.com/article/CA6528666

Design an RTD interface with a spreadsheet →www.edn.com/article/CA6526816

Concerns arise about AMD Puma, analyst suggests AMD may soon be sold →www.edn.com/article/CA6532185

Maxim closing Dallas fab, ceasing RF R&D →www.edn.com/article/CA6527998

Intel, ST claim phase-change-memory prototypes →www.edn.com/article/CA6529570

MIT, TI develop proof-of-concept, energy-efficient microchip →www.edn.com/article/CA6528473

Intel accused of patent infringement in Core 2 Duo by Wisconsin tech transfer office

→www.edn.com/article/CA6530464

Intel, Micron claim world's fastest NAND flash →www.edn.com/article/CA6527820

# DISTRIBUTOR VIEWPOINT

As a companion to "Demand grows for distributor-demand creation" (pg 72), *EDN*'s Suzanne Deffree held a Q&A session with Harley Feldberg, president of Avnet Electronics Marketing. He sits in a unique position from which to assess how the economic slowdown impacts players across the electronics-supply chain.

→www.edn.com/article/CA6530480

## FROM EDN'S BLOGS

There's lots of silicon in photovoltaic cells, but is there any gold for the electronics industry?

From *Practical Chip Design* by Ron Wilson

SEMI, always quick with the attractive luncheon topic, came up with a

house-packing one recently: how electronics companies can make money from the current explosion of investment in solar energy generation. →www.edn.com/080306toc6

#### FEED YOUR NEED

Belly up to the *EDN* Product fEEd, our ongoing buffet of new components, ICs, tools, and more.

→www.edn.com/productfeed

# BY RICK NELSON, EDITOR-IN-CHIEF

# Fractal engineering versus synergy

ngineering is a segmented profession. It divides into highlevel disciplines—mechanical, electrical, civil, chemical, structural, automotive, aerospace, and so on. When you look closely at these high-level disciplines and begin to break them down, you find—fractal-like—that you don't make much headway in reducing the number of areas of engineering specialization available. Just as a fractal divides and repeatedly sudivides

into components that appear to be as complex as the original, engineering disciplines divide and repeatedly subdivide into specialties of increasingly fine yet no less complex granularity.

Take electrical engineering, for example. It breaks down into application segments such as power, communications, consumer electronics, avionics, computers, software, telematics, and medical electronics. For each application area, you can subdivide further into ICs, PCBs (printed-circuit boards), subassemblies, subsystems, and systems. Further, each discipline offers a choice of specialties focusing on R&D, validation, debugging, characterization, production, field installation and repair, and so on.

This segmentation is appropriate. Engineering is too complex for any practitioner to become proficient in more than a few specialization areas, and it's necessary to rely on teams comprising specialists to cover all the facets necessary to get a product to market. Despite the emergence of ESL (electronic-system-level) design, it's difficult for RTL (register-transferlevel) designers, for example, to grasp all the complexities of the aerospace, medical, or automotive products that the ICs they are designing might ultimately populate.

Unfortunately, specialization often results in the formation of walls. The classic wall separates design and test, but, even within test, walls arise that are counterproductive to the cost-effective production of quality products. In the March issue of sibling publication Test & Measurement World, I report on a wall that arises between two test disciplines. In that article, Glenn Woppman, president and chief executive officer of Asset InterTech, commented on his company's acquisition of International Test Technologies: "We've found another wall-[we hope] not as high a wall-between structural test and functional test," he says.

Breaking down the walls between design and test and those between the various test subsets requires a holistic approach toward our subject matter. And holistic approaches, such as the Semiconductor Test Consortium's STIX (Semiconductor Test Interface Extensions) initiative, do exist. The initiative addresses the rising cost and efficiency challenges that impact ATE (automated test equipment), such as enabling greater portability of test collateral through higher level abstraction of user programming, equipment integration, and device interconnect. "[STIX] dramatically increases the potential positive impact of the consortium on the semiconductor industry by extending its influence beyond simply the tester architecture," stated Steve Wigley of the Semiconductor Test Consortium and LTX, writing on www.tmworld.com. "It represents a more holistic approach to addressing the technical and economic issues that affect the entire global-semiconductor-test-supply chain."

Meanwhile, Jack Erickson of Cadence Design Systems addressed power closure, writing in *EDN* that it is "important to address this issue as early and as holistically as possible. The most efficient way is with a central specification of the power-implementation architecture that allows a single change to propagate across the flow. At the end of this exercise, you will have a good idea of the power consumption, timing feasibility, physical feasibility, and functional correctness."

The bottom line is that holistic is good, but even the best efforts of today bring together only the most closely related fractal components of the electrical-engineering profession. And that statement brings up why I'm writing this editorial. I've been writing and reporting for nearly 10 years for Test & Measurement World, most recently serving as Editor-in-Chief. I'll retain that position while also taking on the responsibilities of EDN's Editor-in-Chief. In that role, I'm rejoining the magazine in which I got my start in technical journalism after leaving the engineering profession. The respective EDN and TMW staffs will continue their focus on their specialties but will also concentrate on the synergetic intersections of their respective areas of expertise to bring you the information you need to succeed in this multifaceted world.EDN

As we move forward, I welcome your comments. Contact me at rnelson@reedbusiness.com

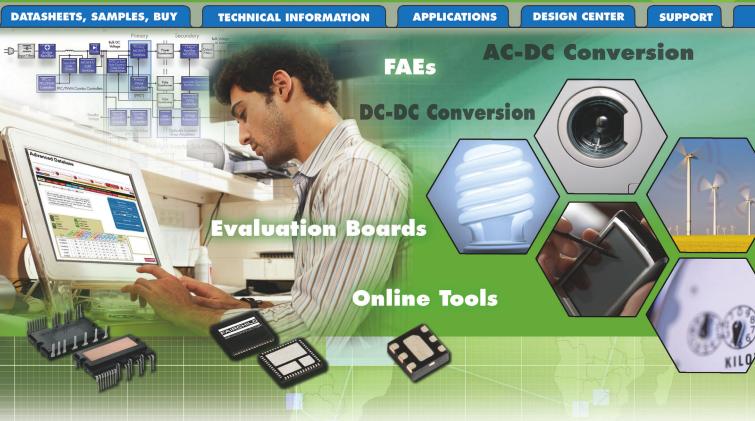

# Save more power. Expend less energy.

# Your engineering resource for energy-efficient solutions.

#### **Power Factor Correction**

PFC Controllers • PFC/PWM Combo Controllers Low-Side Gate Drivers • MOSFET/IGBT Switches

#### **Isolated DC-DC**

PWM Controllers • MOSFETs Integrated Power Switches (FPS<sup>™</sup>) • HVICs Low-Side/Sync Rectifier Gate Drivers Optically Isolated Error Amplifiers Integrated Power Modules (SPM<sup>™</sup>)

#### **Non-Isolated DC-DC**

Multi-Phase PWM Controllers • MOSFETs Integrated Switching Regulators • DrMOS Energy conservation is a global concern, and power engineers face increasingly difficult design challenges. That's why Fairchild—The Power Franchise<sup>®</sup>—is committed to providing the industry's most comprehensive portfolio of power components and support services.

From power analog, power discrete, integrated power modules and optoelectronic products to online tools, FAEs and regional centers staffed by experienced power engineers, we have everything you need to minimize energy consumption in power-sensitive applications. Now both your design and your time are energy-efficient.

For more information about Fairchild's energy-efficient solutions, please visit www.fairchildsemi.com/power.

Saving our world, 1mW at a time™

www.fairchildsemi.com

# Support Across The Board. From Design to Delivery<sup>™</sup>

# Now, you can have it all.<sup>™</sup>

Faster and easier than ever before. Our commitment to customer service is backed by an extensive product offering combined with our supply chain and design chain services – which can swiftly be tailored to meet your exact needs. We have dedicated employees who have the experience to provide the highest level of customer service with accuracy and efficiency. All of our technical experts are factory certified on the latest technologies, providing you the expertise to move projects forward with speed and confidence.

Avnet offers the best of both worlds: extensive product and supply chain knowledge, and specialized technical skill which translates into faster time to market – and the peace of mind that comes from working with the industry's best. Avnet is ranked Best-In-Class\* for well-informed sales reps and knowledgeable applications engineers. Proof that we consistently deliver:

> Industry-recognized Product Expertise

> Specialized Technical Skills

#### Ready. Set. Go to Market.<sup>™</sup> Visit the Avnet Design Resource Center<sup>™</sup> at:

Avnet is a proud sponsor of the Innovation Awards.

Accelerating Your Success<sup>™</sup>

1 800 332 8638 www.em.avnet.com

\*As rated by Hearst Electronics Group, 2006 The Supplier Interface Study. @Avnet, Inc. 2008. All rights reserved. AVNET is a registered trademark of Avnet, Inc.

# ANALOG edge

# Power Supply Design Techniques for FPGAs

#### **Application Note AN-1677**

Tim Hegarty, Applications Engineer

The Xilinx Virtex<sup>™</sup>-5 and Altera Stratix<sup>®</sup> III are families of advanced FPGAs based on 65-nm cores that combine various platforms and speed grades enabling a high level of performance and flexibility. This article discusses FPGA power supply prerequisites as needed by the system designer in terms of the multiple voltage rail and current level requirements, output sequencing, and startup characteristics. Following, a power supply solution based on National Semiconductor's LM1771 and LM3880 is designed that combines high performance, power density and efficiency.

#### **FPGA Power Supply Requirements**

The Virtex-5 or Stratix III FPGAs generally require at least two different voltage rails. The recommended Virtex-5 core voltage, designated  $V_{CCINT}$ , is  $1.0V\pm50$  mV while the Stratix III core rail, denoted  $V_{CCL}$ , can be selected as  $0.9V\pm40$  mV or  $1.1V\pm50$  mV. Depending on the I/O standard being implemented, the Virtex-5 I/O voltage supply,  $V_{CCO}$ , can vary from 1.14V to 3.45V. Thus,  $V_{CCO}$  voltage rails of 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V are feasible. Similarly, Stratix III specifies that the I/O voltage,  $V_{CCIO}$ , can vary from 1.14V to 3.15V, yielding 1.2V, 1.5V, 1.8V, 2.5V, and 3.0V as voltage rail possibilities.

Furthermore, Xilinx defines an auxiliary voltage,  $V_{CCAUX}$ , which is recommended to operate at 2.5V±5% to supply FPGA clock resources. Altera defines additional rails specified for the digital and analog PLL sections, I/O pre-drivers, differential clock inputs, and such. It is required that the power supplies transiently handle larger currents during startup with relatively lower static and dynamic currents during normal operation. The power-up ramp time specification for each voltage rail is 0.2 ms to 50.0 ms for the Virtex-5 and 0.1 ms to 100.0 ms for the Stratix III.

#### **FPGA Power Supply Design Outline**

This proposed FPGA power supply solution is aimed at the Virtex-5 FPGA. A corresponding power supply strategy can be implemented for the Stratix III with subtle changes considering the aforementioned differences.

The power-on sequence recommended by Xilinx is  $V_{\text{CCINT}}, \, V_{\text{CCAUX}},$  and  $V_{\text{CCO}}.$  Although any monotonic

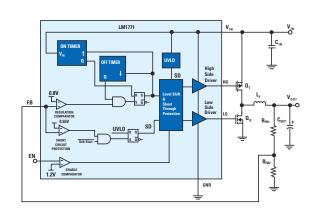

#### Figure 1. LM1771 DC-DC Buck Stage with COT Control Architecture

power-on sequence is tolerated, use of the recommended sequence allows Xilinx to define the minimum inrush current required from the FPGA core, auxiliary and I/O supplies - denoted  $I_{\rm CCINTMIN}$ ,  $I_{\rm AUXMIN}$ , and  $I_{\rm CCOMIN}$ , respectively - to ensure correct power-on and configuration. The solution uses three National Semiconductor LM1771 PWM controllers with power-up and power-down of the individual voltage rails sequenced by a National Semiconductor LM3880 power sequencer.

The LM1771 block diagram with typical external components is presented in *Figure 1*. The LM1771 is an efficient buck converter switching controller available in MSOP-8 and LLP-6 packages and capable of converting an input voltage between 2.8V and 5.5V into a regulated output voltage as low as 0.8V. It drives an external high side PFET and low side NFET and utilizes a constant on-time (COT) control architecture which eliminates the need for an error amplifier and external compensation components. Thus, extremely fast transient load current response is possible. Additionally, the LM1771 features a precision enable pin to facilitate supply sequencing and/or flexibility in setting the operating range of the power supply.

Three LM1771 timing options - designated S, T and U in the part numbering specification - are available which translate to three possible frequency options for a given output voltage. For a given timing option, the switching frequency is independent of input voltage level as the controller input feed-forward feature varies high side switch on-time as a function of input voltage to maintain constant volt-seconds at the switch node.

By virtue of the small-sized package options, the LM1771 allows for a complete power supply design to occupy very little PCB real estate without sacrificing efficiency or performance.

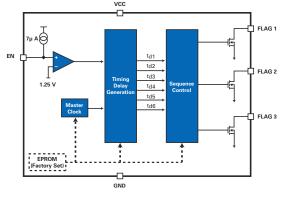

Figure 2. LM3880 Sequencer Block Diagram

The LM3880 sequencer block diagram is presented in *Figure 2*. It is available in a SOT23-6 package and it has three open-drain flag outputs which allow control of the three LM1771 enable pins. Upon enabling the LM3880, the three output flags will sequentially release, after individual time delays, permitting the connected power supplies to startup. The output flags will follow a reverse sequence during power down to avoid latch-up conditions. Standard timing options of 10 ms, 30 ms, 60 ms and 120 ms are available. Additionally, the LM3880 is factory programmable to attain customized timing options combined with six possible power down sequences.

#### National Semiconductor 2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

Mailing Address: PO Box 58090 Santa Clara, CA 95052

#### **FPGA Power Supply Implementation**

The LM1771 and LM3880 based power train schematic is shown in *Figure 3*. For this design, the three buck regulator channels are capable of delivering maximum continuous load currents of 5A, 3A and 3A (I<sub>CCO</sub>, I<sub>CCAUX</sub>, and I<sub>CCINT</sub>, respectively). The I/O voltage is set at 3.3V, but can be easily varied by modifying one of the feedback resistors. The core and auxiliary rails are set at 1.0V and 2.5V, respectively.

The core, auxiliary and I/O regulators use the LM1771S, LM1771T and LM1771U controllers which yield switching frequencies of 606 kHz, 758 kHz and 500 kHz, respectively. Each supply has its own input filter capacitor located as close as possible to the p-channel and n-channel buck and synchronous power FETs. Additionally, a small input bypass capacitor is placed local to each LM1771 IC.

The output filter capacitances on the core and I/O supplies are tantalum based and chosen to present the necessary Equivalent Series Resistance (ESR) to maintain sufficient in-phase ripple at the Feedback (FB) pin. A feed-forward capacitor from  $V_{\rm CCO}$  to the FB pin increases the magnitude of the ripple seen by the LM1771. The output filter capacitance of the auxiliary voltage regulator is ceramic based to minimize the noise level of this rail. A resistor capacitor current sense network across that channel's filter inductor creates a triangular waveform which is ac coupled to the FB node. This circuit can also be utilized in the core and I/O channels if tantalum capacitors are deemed unsuitable and/ or low ESR ceramic capacitors are required either local to the regulator or downstream adjacent to the FPGA.

The filter inductors are designed for large current handling capability with low DC and AC effective resistance to maximize efficiency. The inductance value is conditioned to attain peak-to-peak ripple current of approximately 30% of the rated load current. Further, it is desirable to choose a relatively soft saturation characteristic to handle short duration high current transient events in excess of the rated load current.

TSOP-6 packages are used for the power FETs in the auxiliary rail supply while SO-8 FETs are implemented for the I/O channel regulator. The core voltage supply, given its low duty cycle operating point, has a high side TSOP-6 FET and a low side SO-8 FET.

The LM3880 30 ms timing option, designated -1AB, is recommended. External pull-up resistors are connected to each open-drain flag output.

To read the complete article, visit: national.com/analogedge

#### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark finkelstein@reedbusiness.com

1-781-734-8431

PUBLISHER, EDN WORLDWIDE

Russell E Pratt. 1-781-734-8417:

rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-408-345-4437;

judy.hayes@reedbusiness.com

VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188;

kfield@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-858-748-8418;

rnelson@reedbusiness.com

EXECUTIVE EDITOR

Ron Wilson, 1-408-345-4427;

ronald.wilson@reedbusiness.com

EDITOR IN CHIEF, EDN.COM

Matthew Miller

1-781-734-8446; fax: 1-303-265-3017;

mdmiller@reedbusiness.com

SENIOR ART DIRECTOR

Mike O'Leary

1-781-734-8307; fax: 1-303-265-3021;

moleary@reedbusiness.com

ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@reedbusiness.com

EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor

1-408-345-4424; michael.santarini@reedbusiness.com

EMBEDDED SYSTEMS

Warren Webb, Technical Editor

1-858-513-3713; fax: 1-858-486-3646;

wwebb@edn.com

MASS STORAGE, MULTIMEDIA, PCs AND PERIPHERALS

Brian Dipert, Senior Technical Editor

1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com MICROPROCESSOR, DSPs, TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com NEWS Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com POWER SOURCES. ONLINE INITIATIVES

Margery Conner, Technical Editor

1-805-461-8242; fax: 1-805-461-9640;

mconner@reedbusiness.com

SEMICONDUCTOR MANUFACTURING AND DESIGN

Ann Stefforg Mutschler, Senior Editor

1-408-345-4436; ann.mutschler@reedbusiness.com

DESIGN IDEAS EDITOR

Charles H Small

edndesignideas@reedbusiness.com

SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439;

fax: 1-303-265-3131;

f.granville@reedbusiness.com

ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523;

mbutler@reedbusiness.com

EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024

Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fax: 1-303-265-3198

Melissa Annand, Newsletter/Editorial Coordinator

Contact for contributed technical articles

1-781-734-8443; fax: 1-303-265-3279

Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-303-265-3042

CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

> **COLUMNISTS** Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn; Pallab Chatterjee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164 Linda Lepordo, Production Manager

1-781-734-8332; fax: 1-303-265-3015 EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor in Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

> DENNIS BROPHY Director of Business Development, Mentor Graphics DANIS CARTER

Principal Engineer, Tyco Healthcare CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV

System Architect, Intel

Retired Staff Scientist GABRIEL PATULEA

Design Engineer, Cisco

DAVE ROBERTSON Product Line Director, Analog Devices

SCOTT SMYERS VP Network and System Architecture Division, Sony TOM SZOLYGA

Program Manager, Hewlett-Packard JIM WILLIAMS Staff Scientist, Linear Technology

*EDN*. 225 Wyman St, Waltham, MA 02451. **www.edn.com**. Phone 1-781-734-8000. **Address changes or subscription inquiries:** phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to **www.getfreemag.com/edn**. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# ENERGY DEVICES

# No worries. Your NeoCapacitor is here.

Ultra-low ESR tantalum capacitor: The smart choice for designers and developers

NEC TOKIN America Inc. Headquarters & Western Area Sales Phone: 1-510-324-4110 Chicago Branch (Northeast Sales Office) Phone: 1-847-981-5047 Austin Branch (Southeast Sales Office) Phone: 1-512-219-4040

NEC TOKIN Corporation Global Marketing & Sales Division Phone: 81-3-3515-9220

http://www.nec-tokin.com/english/

# You DESIGN It We BUILD It

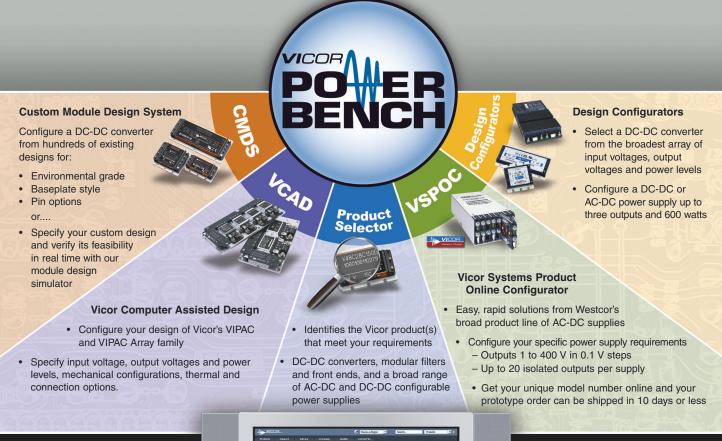

Use the Most Comprehensive Power Design Tools Available

PowerBench gives you the power to specify your own power design solution.

And verify it in real time. All on line.

It's fast, easy, and cost effective!

Visit the Vicor website at www.vicorpower.com/powerbench

Call Vicor Technical Support at 800-927-9474

# vicorpower.com/powerbench

#### EDITED BY FRAN GRANVILLE

# **INNOVATIONS & INNOVATORS**

# Logic-analyzer-based instruments debug, validate MIPI physical layer

gilent Technologies believes that verifying, debugging, and establishing D-PHY (500-Mbps-physical-layer)-based products' specification conformance and interoperability requires specialized tools and that the logic analyzer is the correct platform on which to base such tools. Logic analyzers may at first seem a curious choice because they work with slow and wide parallel buses rather than with fast and relatively narrow serial buses, such as D-PHY. However, serialization and deserialization readily adapt logic analyzers to the higherspeed serial topology. More important, when you use logic analyzers with the appropriate software, they are the most appropriate instruments for displaying packet data in a manner that allows developers to quickly uncover the causes of device-under-test malfunctions.

The MIPI (mobile-industry processor-interface) Alliance's (www.mipi.org) high-speed, low-pin-count, low-power serial-interconnect D-PHY standard originally intended to target a maximum data rate of 500 Mbps per lane. (The D in the acronym is the Roman numeral for 500.) However, the bus is capable of twice that speed: 1 Gbps per lane. Mobile devices-cell phones, cameras, music players, handheld TVs, and the like-represent a huge market for D-PHY, perhaps exceeding a billion units per year.

D-PHY's difficult-to-achieve combination of low cost, low power, high data rate, and compact size bode well for its use in many other types of electronic devices, as well. Implementing D-PHY may, however, prove somewhat more demanding than implementing other high-speed serial protocols: Visibility of some signals can present challenges, and D-PHY lanes are inherently half-duplex to minimize pin count, whereas most other popular highspeed serial standards are full-duplex. You can use two D-PHY lanes to implement full-duplex communication or, if the data rate is amenable, you can reverse a half-duplex lane's transmission direction on the fly.

Agilent's D-PHY product-test offering comprises the N4851A analysis probe with a US list price starting at \$13,561 and the N4861A stimulus probe with a price starting at \$14,566. You use both units with the company's 16900A logic analyzer. Your 16900A should include one or more plug-ins having at least 68 channels. Agilent expects large numbers of developers to require the analysis probe, whereas fewer will require the stimulus probe, which enables the logic analyzer to simulate D-PHYbased hardware. Software that accompanies the probes resides in the 16900A, enabling it to generate D-PHY-specific displays. Both instruments and the accompanying software support the MIPI Alliance's CSI-2 (cameraserial-interface) and DSI (display-serial-interface) D-PHY-based protocols for mobile devices.-by Dan Strassberg

▶ Agilent Technologies, www.agilent.com/ find/mipi. FEEDBACK LOOP "Once again, the authors do a superb job of describing and evaluating the battery-stackvoltage-monitoring issues that I currently have to deal with in my high-volumelithium-ionautomotive application."

-Reader David Kapolka, praises a feature article, in EDN's Feedback Loop, at www. edn.com/article/CA6515356. Add your comments.

The N4851A analysis probe handles deserialization of the MIPI D-PHY 1-Gbps-per-lane physical-layer signals so that the 16900A logic analyzer with one or more plug-ins having at least 68 channels can display the data frames in a manner that reveals the causes of transmission errors.

# pulse

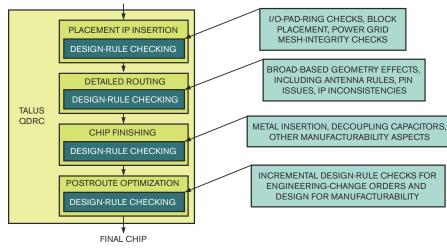

# Magma offers DRC-incremental Talus

agma Design Automation has introduced the Talus **QDRC** (Quartz design-rule-checking) tool to help designers with the placement and routing of ICs. Designers traditionally run DRC after detailed routing to ensure that their designs do not violate any of the targeted foundries' process rules. If they find mistakes, they must transfer the GDSII (Graphic Design System II) files back to placeand-route tools to fix them. After they implement those corrections, the designers often introduce new violations, so they must repeat the process. Streaming the GDSII files between tools can take several hours or even days. A typical design with 10 million instances turns into an approximately 8-Gbyte GDSII file.

Magma hopes to ease and speed the process with the new tool, essentially an integrated DRC within the implementation flow operating on Magma's unified data model. "The major advantage is that you can now do DRC on the implementation database and eliminate the need to stream GDSII into DRC tools to make the changes," says Kevin Walsh, senior vice president of marketing for Magma's physical-verification-business unit. The designs are getting so large that streaming out the files affects

# Using the tool will allow users to cut overall DRC time from days to hours.

data integrity, and you pay the cost of the stream-out time and the time it takes to correct a violation so that you can move on to the next step in the flow. QDRC allows users to do some DRC at the point during which the violations are most likely to occur, which saves stream-out, analysis, and at sign-off time. Because QDRC operates on Magma's memory-resident da-

The Talus QDRC (Quartz design-rule-checking) tool helps designers place and route ICs.

ta model, it allows you to do a true incremental DRC, says Walsh.

Other vendors claim to also have incremental-DRC tools. but Walsh says that competing tools stream out large GDSII files and then generate reports on different parts of the design so users can get to work on those problems. After designers do placement and IP (intellectual-property) insertion, for example, they can run QDRC to do I/O-pad-ring checks, block placement, and powergrid-mesh-integrity checks. After detailed routing, they can do broad-based geometry effects, including antenna rules, pin issues, and IP inconsistencies.

At the chip-finishing stage, they can run checks for metal insertion, decoupling capacitors, and manufacturability aspects. During postroute optimization, they can run incremental DRC for engineering change orders and DFM (design for manufacturability). They can then run the final GDSII files through sign-off DRC using DRC tool, Mentor's (www.mentor.com) Calibre, or a similar tool.

QDRC notes whatever the placer or the router has changed and then checks only those parts of the design. "It allows you to preserve data integrity and efficiency of the operation," says Walsh. Magma claims that using the tool in SOC (system-on-chip) flows will allow users to cut overall DRC time from eight days to roughly 20 hours, that performance is linearly scalable, and that it can run in a small memory footprint. QDRC's prices vary, depending on options, but a stand-alone version sells for \$40,000 to \$60,000.

-by Michael Santarini Magma Design Automation, www.magma-da.com.

# ICs that enable world-class diagnostics for any patient, anywhere.

ADI is a member of Continua Health Alliance, an international group of technology, medical device, and health and fitness industry leaders, dedicated to making personal telehealth a reality

#### Our newest medical innovations

#### AD9271: 8-Channel Ultrasound Receiver

Combined LNA, VGA, AAF, ADC blocks reduce signal path size by 50%, power by 25%. Enables a new level of patient care with accurate images in battery-powered equipment for nontraditional environments.

#### AD8339: Doppler Phase Shifter

Replaces crosspoint switches and analog delay lines, saving up to 75% of board space, 30% of power consumption. Allows increased channel density and CW Doppler capabilities in portable equipment.

#### AD7982: 1 MSPS, 18-Bit, 7 mW ADC

Combines high accuracy, 95% less power, 80% less space than other ADCs. Enables patients to carry their cell-phone sized heart monitor all day long during their hospital recovery.

ADuM240x: iCoupler<sup>®</sup> 4-Channel Digital Isolator Replaces optocouplers with an integrated solution to reduce costs and space up to 60%. Multiple channels of 5 kV reinforced insulation in a single package simplifies design, improves reliability. Approved for medical grade isolation per IEC 60601-1.

# User experience defines the design: ADI defines the possibilities

With Analog Devices ICs inside their designs, medical engineers are dramatically improving the diagnostic experience for patients and practitioners everywhere. That's because ADI offers an industry-leading portfolio of standard and application-tuned amplifiers, data converters, microcontrollers, MEMS, low drop out regulators, and digital isolators with unequaled performance, size, cost, and power advantages. From imaging to monitoring to instrumentation, from medical to consumer to communications-wherever user experience defines the design, ADI is there.

To experience what Analog Devices ICs can do for your designs, visit www.analog.com/medical-ad1.

# pulse

# Open Verification Methodology is ready for download from Cadence, Mentor

emiconductor-designsoftware companies Cadence Design Systems Inc and Mentor Graphics Corp recently announced that their jointly developed OVM (Open Verification Methodology) source code, documentation, and use examples are now ready for free downloading from www.OVMWorld. org. The companies distribute OVM under the standard opensource Apache 2.0 license from the OVM Web site, which is the central point of access for the OVM source code, providing information about partners, events, seminars, training, how-to instructions, and future plans.

OVM on the IEEE Standard 1800-2005 SystemVerilog standard. OVM is the first openlanguage-interoperable, SystemVerilog verification methodology. It comprises a methodology and accompanying library to allow users to create modular, reusable verification environments in which components communicate with each other through standard transactionlevel modeling interfaces.

The OVM also allows intracompany and intercompany reuse through a common methodology and classes for virtual sequences and block-to-system reuse and full integration with other languages that production flows commonly use. Multiple verification platforms support OVM. These platforms suit both novice and expert verification engineers. OVM includes the foundation-level utilities for building advanced object-oriented, coverage-driven verification environments and reusable VIP (verification intellectual property) in SystemVerilog. OVM also reduces the complexity of adopting SystemVerilog by embedding verification practices into its methodology and library, and it reduces the time it takes to create verification environments by integrating plug-andplay VIP and ensuring code portability and reuse.

Robert Hum, vice president and general manager of Mentor's verification-and-test-business unit, notes that OVM represents a major step in protecting customers' investment in verification flows and reusable VIP. Mentor believes that OVM will accelerate the move to SystemVerilog, and provide significant competitive advantages to design-and-verification teams.

A production version of OVM is available now, and the companies plan to add functions this year. Both companies have ensured that the OVM runs on their simulators and allows backward compatibility with their previous environments: Mentor's Advanced Verification Methodology and Cadence's Incisive plan-toclosure methodology.

-by Ann Steffora Mutschler Cadence Design Systems Inc, www.cadence.com. Mentor Graphics, www. mentor.com.

Cadence and Mentor based

# NETWORK-MEDIA PLAYER DRIVES MULTIPLE DISPLAYS

Video displays showing advertising-laden content are popping up in strategic locations, such as gas stations, supermarkets, fast-food dining areas, and airport waiting areas. One company in this market, Apollo Display Technologies, manufactures many of the electronic systems driving these displays, including the recently released ArtistaMe-

The ArtistaMedia network-media controller plays stored or streaming video on flat-panel displays at high-definition resolutions as high as 1080p.

dia single-board networkmedia player.

The board includes a TFT (thin-film-transistor)-LCD controller for playback of videos from a CompactFlash card, 2.5-in. hard-disk drive, or streaming server. You can load or update your stored MPEG-2 or MPEG-4 videos using Ethernet, a CompactFlash card, or a USB stick and play them back in a continuous loop on an unlimited number of displays. Playback is also possible from a streaming-video server without local storage.

ArtistaMedia features onboard audio support and display resolutions of 640×480 pixels to full high-definition 1080p. The board allows direct Ethernet connection of TFT LCDs and eliminates the need for a client PC and operating system at each display. If you don't have or want a network, you can operate ArtistaMedia as a stand-alone player from the supplied CompactFlash card or an optional hard disk.

Other options include an onboard touch controller, a keypad interface, and remote control. The ArtistaMedia player and application software sell for less than \$300 (1000). Delivery is in four to six weeks.

-by Warren Webb Apollo Display Technologies Corp, www.apollo displays.com.

# Babies, bouquets, and big events courtesy of Analog Devices ICs.

#### Our newest camera innovations

#### AD9920A: Highly Integrated Analog Front End (AFE)

Low noise image capture helps to deliver higher quality images at higher ISO settings. This high performance AFE consumes 50% less power than competitive AFEs.

#### SSM2301: Fully Integrated, High Efficiency Class-D Audio Amplifier

Our low power Class-D audio amplifier combines the ability to efficiently deliver more power out, with excellent THD and SNR audio fidelity, for a better remote playback experience.

ADV7520NK: 80 MHz, HDMI Transmitter This HDMI transmitter enables faithful display of your high resolution photos on

display of your high resolution photos on HDTV and consumes a fraction of the standby current of competitive solutions.

# Digital still cameras are all about the user experience that's why more than half have ADI inside

Crisp images. Clear remote audio. Long battery life. When the leading manufacturers of digital still cameras (DSCs) seek to deliver the best user experience, they turn to Analog Devices for its proven credentials as an active partner on the design team. Our years of experience and applications expertise help manufacturers bring the newest DSCs to market on time and on budget. But it's not only camera designers and users who benefit from our extensive portfolio of high performance analog and mixed signal ICs—we're also at the forefront of medical, automotive, communications, and industrial technologies. Wherever user experience defines the design, Analog Devices defines the possibilities.

To experience what Analog Devices ICs can do for your designs, call 1-800-AnalogD or visit *www.analog.com/digitalcameras.*

# pulse

# **RESEARCH UPDATE**

# Fiber-based energy harvester potentially turns garments into generators

Researchers sewed nanowire-encrusted fibers into garments. When someone jostles the garment, the wires produce electricity.

Researchers at the Georgia Institute of Technology have developed a textile-based generator that could enable garments to convert the wearer's movement into electricity to power personal electronic devices. The researchers coax billions of zinc-oxide nanowires to grow radially from a Kevlar fiber, yielding a structure they liken to a bottle brush.

A generator features two such fibers arranged in parallel. One of the fibers gets an additional coating of gold that allows it to serve as the electrode. Employing the same basic principles as an earlier harvester, the generator creates electrical energy via the piezoelectric effect when movement causes the two fibers to rub together (see "Energy harvester generates continuous nanoampere current," EDN, May 24, 2007, pg 28, www.edn.com/article/ CA6442450).

The researchers have measured 4 nA of current and 4 mV of output voltage from a generator employing 1-cm fibers. They estimate that, with design improvements, a square meter of fabric should be able to generate 80 mW. One major barrier to commercialization remains, the team admits: Zinc-oxide is vulnerable to water, so the technology still needs a mechanism for washing-machine survival.

Georgia Institute of Technology, www.gatech.edu.

# Cool-curing polymer simplifies IC fabrication

Rensselaer Polytechnic Institute and Polyset have developed an inexpensive, quick-drying polymer that promises to cut costs for current IC-packaging processes by simplifying the construction of redistribution layers. Meanwhile, the material also shows promise in ultraviolet on-chip nanoimprinting lithography, a potential next-generation IC-patterning technology.

The material, PES (polyset-epoxy siloxane), cures at 165°C, about 35% cooler than the benzocyclobutene and polyimide that chip-packaging companies now rely on for redistribution layers. That reduced need for heat translates directly to savings in overhead costs, according to the researchers. The material matches the other materials in key characteristics, such as thermal stability, low thermal expansion, low dielectric constant, and low leakage current, but surpasses them in water-uptake rate and the ability to adhere to copper.

>Rensselaer Polytechnic Institute, www.rpi.edu.

**Polyset**, www.polyset.com.

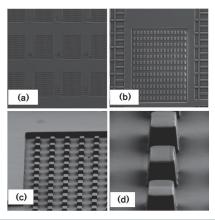

A series of electron-microscope images of a new polymer at 30 microns (a), 10 microns (b), 3 microns (c), and 1 micron (d) show its ability to create well-defined patterns in a UVimprint-lithography application.

# HOLOGRAPHIC DISPLAY HAS A REFRESH RATE OF MINUTES

Scientists at the University of Arizona have developed what they claim is the first updatable, 3-D holographic display. Viewable without special eyewear, the  $4 \times 4$ -in. prototype features a photorefractive polymer between two pieces of electrode-coated glass. The system writes images onto the lightsensitive polymer using laser pulses and an externally applied electric field. The display can produce a new image in about three minutes.

With medical applications in mind, the researchers hope to produce displays as large as 3×3 feet and produce full-color holographic images. University of Arizona, www.arizona. edu.

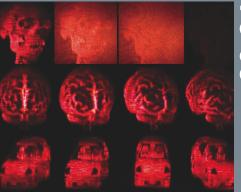

A prototype holographic display shows the erasing process (top row) and 3-D perspective (bottom two rows), which could prove invaluable in military and medical applications.

# 03.06.08

# "Our MCUs, Bios, and Graphics Controllers are changing the way people interact with their cars."

Tommy Tran, Technical Sales Manager, Fujitsu Microelectronics America, Inc.

# AUTOMOTIVE EMBEDDED SEMICONDUCTOR SOLUTIONS

Fujitsu, world-renowned for quality, reliability and support, offers leading-edge embedded semiconductor solutions for the automotive industry.

## **MICROCONTROLLERS**

- 8-, 16-, 32-bit MCUs with CAN, LIN support

- Reliable and large embedded Flash memory

- 28- to 208-pin packages

## **IN-CAR NETWORK**

- Single-chip FlexRay<sup>™</sup> controller and ASSP

- IDB-1394 S400 single-chip controller

## **GRAPHICS DISPLAY CONTROLLERS**

- 3D with alpha blending

- Video input with image resizing

- Wide temperature range

# **BIOMETRIC SENSORS**

- Standard CMOS technology

- Clear 500-dpi images

- Rugged, super-thin design

- World-class matching algorithm

For more information, call (800) 866-8608 or visit http://us.fujitsu.com/micro

SIGNAL INTEGRITY

$R_{T} = 150$

1.5

IC<sub>1</sub> (V)

0

100

50

VIRTEX-4

HSTL I

1 nSEC/DIV

VOH

HYPERLYNX LINESIM

VERSION 77

# BY HOWARD JOHNSON, PhD

# Z<sub>MIN</sub>, a very special value

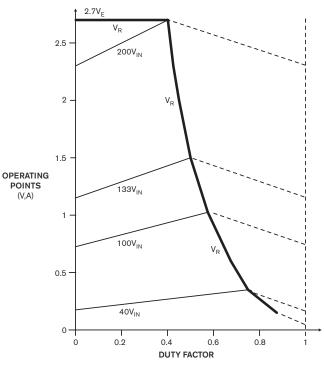

The driver in **Figure 1** precisely meets its specified high- and low-output-voltage levels with a termination resistance of  $25\Omega$ . If you increase the resistor's value, the circuit becomes progressively easier to drive, making the waveform exceed the specs in both directions. If you decrease it, the driver fails to produce a sufficiently large signal.

Resistor  $R_T$  controls the gain of the circuit, and the termination voltage controls the dc offset. Between gain and offset, you have everything you need to effect complete control over the output waveform, within reason.

When you design an end-terminating circuit, you must select an effective termination resistance large enough to guarantee that the driver can produce a full-sized output swing and then set the effective termination voltage to center the waveform so it crosses both the high- and the lowoutput voltages. No matter what topology you use to implement the final circuit, whether it looks like a resistorand-battery arrangement or a voltagedivider (split-terminator) structure, the gain and offset constraints apply.

The smallest value termination resistance for which the output swing can, with a perfect setting of termination voltage, just barely touch both the high- and the low-output voltages, with no tolerance for error and no margin, is a very special value I call  $Z_{\rm MIN}$  (minimum impedance). Understanding this value is the secret to successful end-termination design.

The value of the minimum termination impedance derives from a general output-current relation. Simply, the driver output current always equals the voltage drop across the resistor divided by its value in ohms. If you correctly set the minimum impedance, then, when the driver pulls high to the highoutput voltage, the current precisely equals the high output current:

$I_{OH} = (V_{OH} - V_T)/Z_{MIN}, \quad (1)$ where  $I_{OH}$  is the high output current,  $V_{OH}$  is the high output voltage,  $V_T$  is the termination voltage, and  $Z_{MIN}$  is the minimum impedance.

In the low state, you get a similar relationship:

$$\begin{split} I_{OL} = & (V_{OL} - V_T) / Z_{MIN}. \quad (2) \\ \text{Subtract Equation 2 from Equation 1:} \\ I_{OH} - I_{OL} = & (V_{OH} - V_{OL}) / Z_{MIN}. \quad (3) \\ \text{Solving for } Z_{MIN} \text{ yields the "golden"} \\ \text{equation of end-termination design:} \end{split}$$

$Z_{MIN} = (V_{OH} - V_{OL})/(I_{OH} - I_{OL}).$  (4)

Equation 4 says that the minimum impedance equals the spread in voltage between the high-output voltage and the low-output voltage divided by the spread in current between the high-output current and the lowoutput current. Your driver can never successfully drive any load with a long-term impedance of less than the minimum impedance.

When working **Equation 4**, pay attention to the polarity of the currents.

Source current is positive. Sinking current is negative. For example, if a driver sources and sinks 25 mA, then its spread is (25-(-25))=50 mA.

Suppose that the minimum impedance for your driver works out to  $60\Omega$ . I would not use an end termination with that value. It leaves no room for component tolerance. Other effects, such as temperature and age variation in the termination voltage, can knock the circuit out of specification. You should use a slightly larger value, such as  $70\Omega$ .

On a 50 $\Omega$  transmission line, a 70 $\Omega$  termination won't be perfect. It will cause a reflection of (70-50)/(70+50)=16.7%. If that's too much for your voltage-margin budget, then consider raising the transmission-line impedance. Bring the line impedance up to perhaps 60 or 70 $\Omega$ . The closer you bring the transmission-line impedance to the termination resistance, the better your system will work.

The optimal value for the termination resistance is just a little higher than the minimum impedance to account for tolerances, with a transmission-line impedance as close as practical to the termination resistance. **EDN**

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

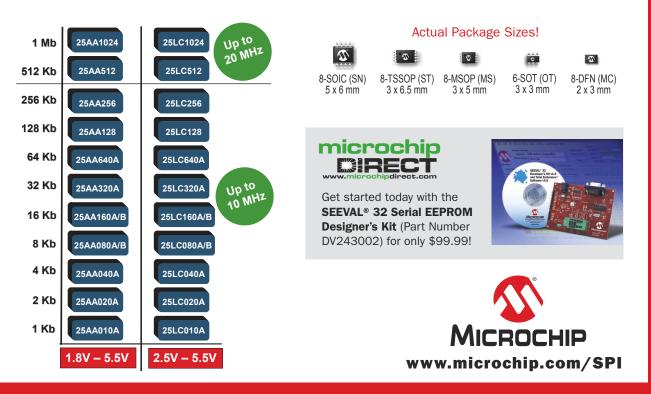

# The Fastest SPI Serial EEPROMs in the Industry

# Speed • Quality • Reliability • Availability

Microchip provides SPI serial EEPROMs across a wide memory-density range (1 Kbit - 1 Mbit), which are specified to operate over an extended temperature range (up to 125°C). These devices provide over 1 million erase/write cycles and 200-year data retention.

Microcontrollers • Digital Signal Controllers • Analog • Serial EEPROMs

# BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

# Know your IP provider

ith the shortened time to market for consumer and industrial products and the rapid introduction of new process technologies through the foundry market, there is a rash of new IP (intellectual-property) companies offering substandard and misrepresented products. The trend was inevitable in a grow-

ing marketplace. However, the presence of weak IP companies impacts the viability of the properly engineered and supported IP companies.

Additionally, countless chips and end products will fail to work, have reliability issues, and be difficult to debug as a result of these substandard IP blocks.

The selection of the IP provider and the blocks and functions involved is *not* just a business issue. Although business aspects are always important, for IP modules built in less-than-130nm processes, the validation of the IP and the infrastructure supporting it are key criteria. Just how important? Currently, one of the largest causes of SOC (system-on-chip) failures from foundry shuttle runs or prototype runs is the use of unqualified IP in the design.

Every SOC builder's checklist should include some IP-provider selection criteria. First, does the company have legitimate licenses for the EDA tools it is providing kits for? Many companies are outsourcing major portions of the design to Eastern Europe, India, and China, where software piracy is very visible. Pirated software tends to lack the current patches or the metadata that make it compatible with current legitimate code and could result in noncorrectable problems in design-for-manufacturing and mask-data-preparation steps.

# It is the norm in the current global design community for the development site to be separate from the point of sale.

Second, does the company have a history of commercially manufacturing the IP or parts? A number of companies are promoting silicon-proven experience when the only actual silicon they have run has been government-funded or -subsidized test chips on Defense Department or university processes. In most cases, the IP that a company sends to a fab on an MPW (multiproject wafer) under a military contract is not releasable to others because of licensing issues. In these cases, the vendor claiming silicon-tested IP is actually sending modified, processmigrated, and untested IP to its commercial customers-only "validated" by these other, different designs.

Third, does the company's engineering team have the experience and support level you need? The larger IP providers, such as ARM, Synopsys, and Mentor, all have standard documented application and design support for their IP that includes device and RTL integration, tool integration, application verification, physical implementation and verification, and test development. The smaller IP providers are sometimes staffed only by recent university graduates and a research support team that cannot support the IP in a context of an SOC, because they have little to no real chip-building or CAD-tool-flow experience.

TAPFOUT

Fourth, does the company have the designers of its IP in-house? One of the basic assumptions is that the IP provider you are dealing with actually created the block you are licensing. In reality, some IP companies are merely brokering blocks that contractors created, IP it acquired from other companies, or blocks that are process migrations from pirated IP libraries that are floating around the industry.

This repackaging is difficult to identify at the data level and requires finding an IP company that will identify the location of its design group and offer an avenue for the end licensee to reach this group to modify or integrate the IP block in its SOC design. In this context, in-house does not necessarily mean the same location; it is the norm in the current global design community for the development site to be separate from the point of sale. However, the designers should be accessible not moonlighting engineers in importor export-restricted countries.

Look for additional guidelines and physical-design keys in a future article.EDN

Contact me at pallabc@siliconmap.net.

#### MORE AT EDN.COM

+ Go to www.edn.com/080306pc and click on Feedback Loop to post a comment on this column.

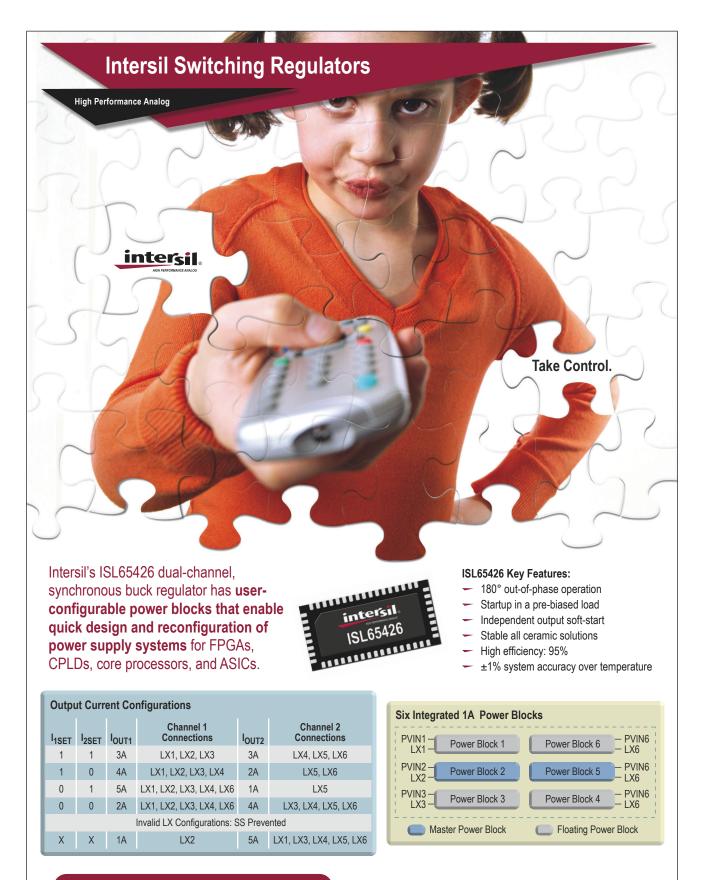

©2007 Intersil Americas Inc. All rights reserved. The following are trademarks or services marks owned by Intersil Corporation or one of its subsidiaries, and may be registered in the USA and/or other countries: Intersil (and design) and i (and design). HIGH PERFORMANCE ANALOG

# The **2008** catalog

America's Electronic and Electromechanical Distributor of Choice.

We do more than take your order.

- 2,200 pages of product solutions

- Over 150,000 products at your fingertips

- More than 300 world class suppliers

call or click for your free copy of the 2008 Allied catalog

1.800.433.5700

alliedelec<sub>k</sub>com

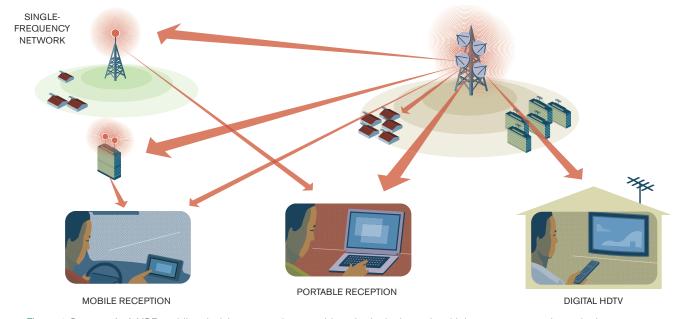

IF YOU THINK CELLULAR'S THE ONLY WAY YOU'LL CATCH ON-THE-GO TELEVISION IN THE FUTURE, THINK AGAIN. OVER-THE-AIR BROADCASTERS AND SATEL-LITE-BASED-SERVICE PROVIDERS HOPE TO CATCH THE MOBILE-TV WAVE AND RIDE IT TO FISCAL SUCCESS.

BY BRIAN DIPERT • SENIOR TECHNICAL EDITOR

# MOBILE Image: Mail of the second state o

DN's recent mobile-television article focused mostly on transmission protocols amenable—for technical reasons, business reasons, or both—to cellular handsets, including DVB-H (digital-video-broadcasting-handheld), EVDO (evolutiondata optimized), UMTS (universal-mobile-telecommunications system), and MediaFlo (**Reference 1**). However, as Japan's 1seg and South Korea's T-DMB (terrestrial-digital-multimedia-

broadcasting) networks suggest, it's possible to graft support for conventional digital-television broadcasts onto a mobile phone if the economics justify the surgery. And, as the earlier article

points out, it's not a foregone conclusion that the cellular handset will be the predominant means by which viewers tune into mobile TV (see **sidebar** "More ahead").

Any secondary application that drains the battery and precludes subsequent access to the unit's primary application making and taking telephone calls, for example—will likely receive a cool reception by consumers, especially if it's also one that considerably adds to the unit's price tag. Mobile TV has both qualities. A significant disparity between all-in-one widget aspirations and feasible reality opens the door to system alternatives with more focused functions and to a lengthier list of alternative infrastructure approaches.

#### A NETWORK COUNTERATTACK

Before last month's 3GSM (Third Generation Groupe Spéciale Mobile) Congress conference in Barcelona, Spain, Michael Rayfield, handheldbusiness-unit general manager at Nvidia, agreed—at least from a technical standpoint—with what the material in **Refer**-

ence 1 points out: that generational improvements in DVB-T's (digital-videobroadcasting-terrestrial) power-consumption characteristics might obviate the need for a late-arriving DVB-H descendant. However, from a business perspective, subscription-supported cellular carriers control DVB-H spectrum, whereas DVB-T signals come from advertisingrevenue-based local and nationwide television broadcasters.

According to Rayfield, no cellularservice provider and, therefore, no hardware partner will embed handset support for a feature unless, when a consumer uses the feature, it translates into tangible revenue for the carrier. "The last time the cellular-service providers added a low- to no-revenue feature was the camera phone." Rayfield also pointed out that cellular phones don't tune in AM- or FM-radio transmissions. "And they didn't add the camera feature out of charity; they thought it'd be highly profitable, although it didn't turn out that way," he said (**Reference 2**).

The cellular-versus-broadcast-service tug of war that Rayfield suggests is occurring in Europe is also likely to exist in any country in which revenue- and profit-fueled open-market conditions determine business success or failure that is, when a government or another organization doesn't heavily subsidize the service. The struggle is occurring in

#### AT A GLANCE

Battery-draining concerns, along with consumers' preferences for free, albeit advertising-supported content, open the door to noncellular mobile-television options.

Several proposals, now operating in prototype trials, aspire to augment ATSC (Advanced Television Systems Committee) with portable capabilities.

L's unclear whether cellular carriers' and their hardware partners' future handsets will support ATSC-M/H (ATSC-Mobile/Handset).

Satellite-delivery schemes are location-generic but have plenty of competition and, in handheld configurations, come with power-consumption shortcomings.

the United States, where over-the-air-TV broadcasters have over time increasingly seen their direct-access audience shrink; consumers are instead indirectly viewing broadcasters' content using cable, IPTV (Internet Protocol television), satellite, and other service intermediaries. In such a scenario, lucrative advertising revenue flows directly to the intermediaries, not to the broadcasters, and content-licensing fees don't make up the shortfall.

Now, another set of potential delivery intermediaries, the cellular-service pro-

viders, is entering the picture. Several US broadcast-network and local-affiliate representatives paint the mobile-phone carriers as competitors, though none of them will go on record as saying so. This reluctance is no surprise, because the carriers are also these networks' and affiliates' partners, and a public statement critical of that relationship might adversely affect the licensing-fee-revenue flow. Despite that reluctance, the networks and affiliates do worry about the long-term fiscal impact of having only a supporting role in the mobile-TV market of the future. That concern explains the vigorous, ongoing industry development of the ATSC-M/H (Advanced Television Systems Committee-Mobile/ Handset) specification.

#### ATSC SHORTCOMINGS

The developers of 8-VSB (eightlevel-vestigial-sideband)-based ATSC designed it with exclusively stationary reception in mind, unlike its COFDM (coded-orthogonal-frequency-divisionmultiplexing)-based peers. As a result, ATSC is prone to environmentally induced factors, such as multipath-signal distortion, which causes egregious mobile-TV reception. I was witness to an example of this bad reception during a Samsung-hosted bus ride in Las Vegas at last year's NAB (National Association of Broadcasters) Conference. Sin-

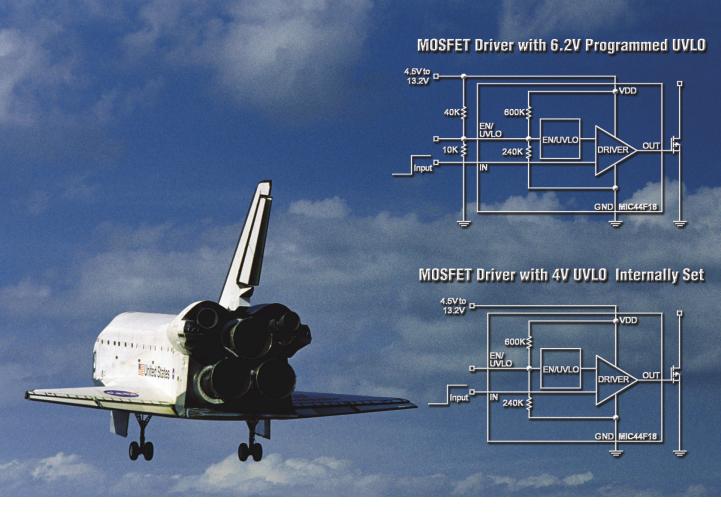

# **Driving To New Frontiers...** Micrel's Ultra High-Speed MOSFET Drivers

# 6A, 10ns Rise/Fall Times, Ultra High-Speed MOSFET Drivers

THE MIC44F18, MIC44F19 and MIC44F20 are high-speed MOSFET drivers capable of sinking and sourcing 6A for driving capacitive loads. With delay times of less than 15ns and rise times into a 1000pf load of 10ns, these MOSFET drivers are ideal for

driving large gate charge MOSFETs in power supply applications. For more information, contact your local Micrel sales representa-

For more information, contact your local Micrel sales representative or visit us at www.micrel.com/ad/mic44f18\_19\_20. Literature 1 (408) 435-2452 Information 1 (408) 944-0800

| MIC44F18 | Non-Inverting                       |

|----------|-------------------------------------|

| MIC44F19 | Inverting Output High When Disabled |

| MIC44F20 | Inverting Output Low When Disabled  |

## Good Stuff:

- ♦ 6A driving capability

- ◆ 10ns rise/fall time into 1000pf load, 15ns propagation delay

- ◆ 4.5-13.2V input voltage range

- Programmable UVLO/Precision enable

- Thermally enhanced packages:

- MLF<sup>™</sup>–8 (2 x 2mm)/MSOP-8

- ◆ Latch-up protection to >500ma reverse current on output pin

#### **Applications:**

- Switch-mode power supplies

- ◆ Secondary side synchronous rectification

- Relay and solenoid driver

@ 2008 Micrel, Inc. All rights reserved. Micrel is a registered trademarks of Micrel, Inc. MLF is a registered trademark of Amkor Technologies.

www.micrel.com

clair-owned TV station KVMY was broadcasting ATSC-compliant images, which in-vehicle electronics received and displayed on an LCD on the rear wall of the bus. Whenever the bus was moving, artifacts corrupted the images, and, when the bus speeded up, the images disappeared altogether, despite the bus-based receiver's cognizance of the SRS (supplementary-reference-sequence) bit stream and the use of multiple diversity-reception antennas.

Two LCDs next to that one, along with Samsung-supplied UMPC (ultramobile-personal-computer) handheld systems, showed no artifacts, no matter how fast the bus was moving. Samsung based them on A-VSB (advanced-VSB) technology, which Samsung and Rohde & Schwarz developed. A-VSB redirects a portion of the 19.2-Mbps ATSC digital-broadcast stream away from its traditional functions-carrying Dolby Digital audio and MPEG-2 video information-instead allocating it for two mobile purposes. One purpose is a 1-Mbps SRS bit stream to assist a receiver in remaining "locked" onto the broadcast signal while in the presence of dynamic interference. The other is a variablebit-rate turbo code for EDAC (error detection and correction) and error concealment within the audio and video streams.

Samsung privately showed A-VSB

# MORE AHEAD

The technical capabilities and economic attributes of 4G cellular networks, such as LTE (long-term-evolution) and UMA (unlicensed-mobile-access) may make them more amenable to mobile-TV transmission than their 3G predecessors, WiMax holds similar potential, and Sprint is poised to soon launch it in the United States. For more information on all of these technologies, see EDN's April 3, 2008, issue, whose publication will coincide with the CTIA (Cellular **Telecommunications Industry** Association) Wireless show.

Figure 2 Sirius's Backseat TV made its initial preinstalled appearance in a variety of Chrysler 2008-model-year vehicles and is also available aftermarket.